单片机篮球比赛计分器课程设计_基于单片机的篮球比赛计时计分器程序研究

1.篮球比赛计时器设计 加 原理图

2.急 求篮球计数器设计报告

二篮球比赛计分器系列

[1]红外无线遥控篮球比赛计分器

可定制实现的功能:

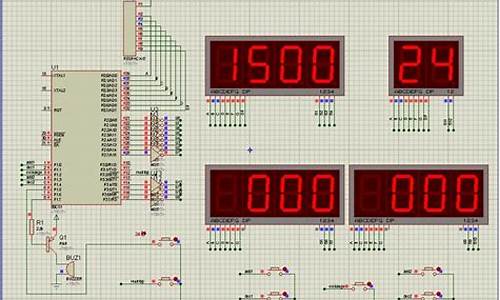

通过红外遥控器进行设定比赛时间,可以实现开始、暂停、加减分、结束等功能,具有24S时间功能。

☆已作出的实物优酷视频演示地址:

单片机篮球比赛计时器(按键版本)

可定制实现的功能:

简单实现篮球比赛计时功能。

☆已作出的实物优酷视频演示地址:

手机蓝牙无线遥控篮球比赛记分牌

简介:同红外版本一样,通过手机蓝牙APP来实现无线遥控篮球比赛计分系统的设计。可以设定时间,遥控比赛开始,暂停,结束等,加减分等功能。

☆已作出的实物优酷视频演示地址:

style="font-size: 18px;font-weight: bold;border-left: 4px solid #a10d00;margin: 10px 0px 15px 0px;padding: 10px 0 10px 20px;background: #f1dada;">篮球比赛计时器设计 加 原理图

MAX PLUS II 主要是提供你的一些器件提取

你只要自己找到连接的电路图就能用了

MAX PLUS II的基础操作还是很简单的

在篮球比赛中,规定了球员的持球时间不能超过30秒,否则就犯规了。本课程设计的“篮球竞赛30秒计时器”,可用于篮球比赛中,用于对球员持球时间30秒限制。一旦球员的持球时间超过了30秒,它自动的报警从而判定此球员的犯规。

本设计主要能完成:显示30秒倒计时功能;系统设置外部操作开关,控制计时器的直接清零、启动和暂停/连续功能;在直接清零时,数码管显示器灭灯;计时器为30秒递减计时其计时间隔为1秒;计时器递减计时到零时,数码显示器不灭灯,同时发出光电报警信号等。

整个电路的设计借助于EWB5.12仿真软件和数字逻辑电路相关理论知识,并在EWB5.12下设计和进行仿真,得到了预期的结果。

设计原理

30秒计时器的总体参考方案框图如图2-1所示。它包括秒脉冲发生器、计数器、译码显示电路、报警电路和辅助时序控制电路(简称控制电路)等五个模块组成。其中计数器和控制电路是系统的主要模块。计数器完成30秒计时功能,而控制电路完成计数器的直接清零、启动计数、暂停/连续计数、译码显示电路的显示与灭灯、定时时间到报警等功能。

秒脉冲发生器产生的信号是电路的时钟脉冲和定时标准,但本设计对此信号要求并不太高,故电路可采用555集成电路或由TTL与非门组成的多谐振荡器构成。

译码显示电路由74LS48和共阴极七段LED显示器组成。报警电路在实验中可用发光二极管代替。

设计方案

分析设计任务,计数器和控制电路是系统的主要部分。计数器完成30s计时功能,而控制电路具有直接控制计数器的启动计数、暂停/连续计数、译码显示电路的显示和灭灯功能。为了满足系统的设计要求,在设计控制电路时,应正确处理各个信号之间的时序关系。在操作直接清零开关时,要求计数器清零,数码显示器灭灯。

当启动开关闭合时,控制电路应封锁时钟信号CP,同时计数器完成置数功能,译码显示电路显示“30”字样;当启动开关断开时,计数器开始计数;当暂停/

急 求篮球计数器设计报告

NBA篮球24秒倒计时本设计是以555构成震荡电路,由74LS192来充当计数器,构成NBA24秒倒计时电路。该电路简单,无需用到晶振,芯片都是市场上容易购得的。设计功能完善,能实现直接清零、启动和暂停/连续计时,还具有报警功能一、设计原理与电路

原理方框图图:包括秒脉冲发生器、计数器、译码与显示电路、报警电路和控制电路(辅助时序控制电路)等五个部分组成。计时电路递减计时,每隔1秒钟,计时器减1其中计数器和控制电路是系统的主要部分。计数器完成24秒计时功能,而控制电路完成计数器的直接清零、启动计数器、暂停/连续计数、译码显示电路的显示与灭灯、定时时间到报警等功能。当计时器递减计时到零(即定时时间到)时,显示器上显示00,同时发出光电报警信号。秒脉冲发生器产生的信号是电路的时钟脉冲和定时标准,但本设计对此信号要求并不是太高,电路采用555集成电路或由TTL与非门组成的多谐振荡器的构成。

译码显示电路用74LS48和共阴极七段LED显示器组成。报警电路在实验中可用发光二极管代替。

二、模块说明:

○18421BCD码递减计数器

计数器选用中规模继承74LS192进行设计较为简便,74LS192是十进制可编程同步加/减计数功能。下图是74LS192外引线排列图与功能表:

工作原理:当 =1,CR=0时,若时钟脉冲加入到 端,且 =1,则计数器在预置数的基础上完成加计数功能,当加计数到9时, 端发出进位下跳脉冲;若时钟脉冲加入到 端,且 =1,则计数器在预置数的基础上完成减计数功能,当减计数到0时, 端发出借位下跳变脉冲。由74LS192组成的二十四进制递减计数器如下图,其预置数为N=(0010 0100)8421BCD=(24)。它的计数原理是:只有当低位 1端发出借位脉冲时,高位计数器才作减计数。当高、低位计数器处于全零,且 =0时,置数端 2=0,计数器完成并行置数,在 端的输入时钟脉冲作用下,计数器再次进入下一循环减计数。○2555振荡模块

如右图,由NE555构成的多谐振振荡器。接通电源后,电容C2被充电,Vc上升,当Vc上升到2/3Vcc时,触发器被复位,同时放电BJTT导通,此时V0为低电平,电容C通过R5和T放电,使Vc下降,当下降至1/3Vcc时,触发器又被置位,V0翻转为高电平。电容器C的放电时间为:

当C放电结束时,T截止,Vcc将通过R5和Rw、R4向电容器充电,Vc由1/3Vcc上升到2/3Vcc所需时间为:

当Vc上升到2/3Vcc时,触发器又发生翻转,如此周而复始,在输出端就得到一个周期性的方波,其频率为:

在这里我们选择R5=68K,C2=10uf,只要调节Rw 7K即可输出1HZ,达到要求。

○3辅助时序控制电路

操作“清零”开关时,计数器清零。闭合“启动”开关时,计数器完成置数,显示器显示24断开“启动”开关,计数器开始进行递计数。电路图中,当开关S1合上时, =0,74LS192进行置数;当S1断开时, =1,74LS192处于计数工作状态。开关S2是时钟脉冲信号CP的控制电路。当定时时间未到时,74LS192的借位输出信号 2=1,则CP信号受“暂停/连续”开关S2的控制,当S2处于“暂停”位置时,门G3输出为0,门G2关闭,封锁CP 信号,计数器暂停计数;当S2处于连续位置时,门G3输出1,门G2打开,放行CP信号,计数器在CP作用下,继续累计计数。当定时时间到时, 2=0,门G2关闭,封锁CP信号,计数器保持零状态不变。

三、调试

做完板后发现暂停有毛刺现象,故补充另一开关来控制暂停,效果好转。以下是其电路:

四、后语

不足:本电路设计简单,而且能很好地达到设计要求,但由于555产生的脉冲精确值比较低,这是本电路最大的不足。

改进方法:可以使用晶振,然后进行分频(如用4060)。

《数字逻辑与数字系统》 课程设计 设计题目:篮球比赛计时器 一、设计任务和基本要求:1.篮球比赛上下半场各20分钟,要求能随时暂停,启动后继续计时,一场比赛结束后应可清零重新开始比赛。2.计时器由分、秒计数器完成,秒计数器为模60,分计数器应能计至40分钟。3. “分”、“秒”显示用LED数码管。4.人工拨动开关来控制计时器的启动/暂停。5.半场、全场到自动会有相应的提示。 二、实验所需要硬件与软件:?0?1 数字电路实验系统?0?1 可编程器件(PLD)及连接导线?0?1 PC计算机?0?1 ispLEVER编程软件 三、题目分析:本题比较简单,要求中的篮球比赛上下半场各20分钟,可以参考数字时钟,篮球比赛计时器相当于一个可以暂停的,能整点报时的时钟设计。 四、设计思想及说明:采用加法器与计数器的思想,分别设计一个M60(秒)和一个M20(分)计数器,由分频产生1HZ的脉冲信号,上下两场可以是两个完全一样的20分钟的计时器,中场及终场是喇叭发声提醒,并在计数器中加入暂停和复位设置,控制脉冲的输入,随时暂停与复位。 五、设计步骤:此题设计主要是ISP编程设计,我们主要用了分频(产生1hz信号)、暂停(pause)、复位(clear)以及加法器这几个模块的程序组成了整个篮球比赛计时器的设计。 六、使用说明:跟据程序连接好实验电路后,输入10KHZ的信号分频得到1HZ的脉冲,计时器开始运作后,我们用pause和clear控制暂停和复位。当pause为高电平,clear为高电平时,计数器工作。我们把pause改为低电平,则计数暂停,再把pause改为高电平,计数继续。若clear改为低电平,计数清零。当计时器到达20分时,结束半场或整场结束,喇叭鸣叫报警。 七、源程序代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all; entity basketball isPORT(pause:IN std_logic;clear:IN std_logic;clk:IN std_logic;sound:OUT std_logic;s2:OUT std_logic_vector(3 downto 0);s1:OUT std_logic_vector(3 downto 0);m2:OUT std_logic_vector(3 downto 0);m1:OUT std_logic_vector(3 downto 0));END basketball; architecture behave of basketball isSIGNAL clk1:std_logic;beginPROCESS(clk)VARIABLE cnt:integer range 0 to 49999;begin IF(clk'EVENT AND clk = '1') THEN if(cnt=49999) THEN cnt:=0; clk1<=not clk1; else cnt:=cnt+1; end if; end IF;END PROCESS; PROCESS(clk1)VARIABLE tms2,tms1,tmm2,tmm1:std_logic_vector(3 downto 0);VARIABLE ebit,tmsound:std_logic;begin if(tmm1="0010"and tmm2="0000"and tms1="0000" and tms2="0000") THEN tmsound:='1'; elsif(tmm1="0100"and tmm2="0000"and tms1="0000"and tms2="0000") THEN tmsound:='1'; elsif(tmm1="0001"or tmm1="0000")THEN tmsound:='0'; elsif(tmm1="0010"or tmm1="0011")THEN tmsound:='0'; end if;IF(clear='0') THENtms2:="0000";tms1:="0000";tmm2:="0000";tmm1:="0000";ELSIF(clk1='1'AND clk1'EVENT AND tmm1/="0100"AND tmsound='0') THENif(pause='1')THENebit:=tms1(2) and tms1(0) and tms2(3)and tms2(0) and pause;if(ebit='1') then if(tmm2="1001") then tmm2:="0000"; tmm1:=tmm1+1; else tmm2:=tmm2+1; end if;end if; if(tms2="1001") then tms2:="0000"; if(tms1="0101") then tms1:="0000"; else tms1:=tms1+1; end if; else tms2:=tms2+1; end if;end if;end IF; s2<=tms2; s1<=tms1; m2<=tmm2; m1<=tmm1; sound<=tmsound;end PROCESS;end behave;